### Noisy Logic

## Exploiting the Interplay between Nonlinearity and Noise for Computation

### Sudeshna Sinha

Indian Institute of Science Education and Research (IISER), Mohali

homepage: http://www.imsc.res.in/ $\sim$ sudeshna

Cooperative behavior between noise and dynamics often produces interesting, often counter-intuitive, physical phenomena

such as Stochastic Resonance

This effect has been demonstrated in many physical systems, and is thought to occur in nature

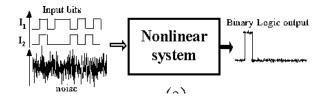

Here we investigate the response of a nonlinear system, possessing several simultaneously stable states, to a stream of input signals

We find that, in an optimal band of noise, the output consistently is a logical combination of the input signals:

Logical Stochastic Resonance (LSR)

K. Murali and Sudeshna Sinha, Nonlinear Dynamics (Narosa, 2009)

K. Murali, Sudeshna Sinha, W.L. Ditto, A. Bulsara Physical Review Letters, March 2009 Our motivation stems from an issue that is receiving considerable attention today:

As computational devices and platforms continue to shrink in size we are increasingly encountering fundamental noise characteristics that cannot be suppressed or eliminated Hence, an understanding of the cooperative behavior between a device noise-floor and its nonlinearity is bound to play an increasingly crucial, even essential role in the design and development of future computational concepts and devices

Reliable Logic Circuit Elements that Exploit Nonlinearity in the Presence of a Noise-Floor

Consider a general nonlinear dynamic system, given by

$$\frac{dx}{dt} = F(x) + I + D \eta(t)$$

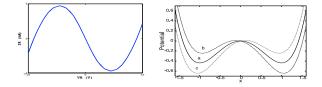

F(x): Generic nonlinear function giving rise to a potential with distinct energy wells

I : low amplitude input signal

$\eta(t)$  is an additive zero-mean Gaussian noise with variance 1 Parameter *D* gives the noise strength Example of cubic nonlinearity :

$$\dot{x} = 2x - 4x^3 + I + D \eta(t)$$

Effective Potential : bistable

Potential minima at  $x_{-} \sim -1$  (lower well) and  $x_{+} \sim 1$  (upper well)

3

Image: A matrix and a matrix

Logical input-output correspondence is achieved by encoding N inputs in N square waves

Specifically, for two logic inputs : drive the system with a low amplitude signal *I*, taken to be the sum of two trains of aperiodic pulses:

$I = I_1 + I_2$

with  $I_1$  and  $I_2$  encoding the two logic inputs

The logic inputs can be either 0 or 1

```

Giving rise to 4 distinct logic input sets (I_1, I_2):

```

```

(0,0),(0,1),(1,0),(1,1)

```

Input sets (0, 1) and (1, 0) give rise to the same *I*, and so the 4 distinct input conditions  $(I_1, I_2)$  reduce to 3 distinct values of *I*

Hence, the input signal *I*, generated by adding two independent input signals, is a 3-level aperiodic waveform

The Output of the system is determined by its state

For instance, the output can be considered a logical 1 if it is in one well, and logical 0 if its in the other well

Specifically for a system with potential wells at  $x_+ > 0$  and  $x_- < 0$

- Output is 1 when the system is in the well at  $x_+$

- Output is 0 when the system is in the well at  $x_{-}$

Hence, when the system switches wells, the output is toggled

Noisy nonlinear system forced by an input signal yielding a logic output

We will demonstrate that one observes, for a given set of inputs  $(I_1, I_2)$ , a logical output from this nonlinear system, in accordance with the truth tables of the basic logic operations in an optimal band of noise

| Input Set $(I_1, I_2)$ | OR | AND | NOR | NAND |

|------------------------|----|-----|-----|------|

| (0,0)                  | 0  | 0   | 1   | 1    |

| (0,1)/(1,0)            | 1  | 0   | 0   | 1    |

| (1,1)                  | 1  | 1   | 0   | 0    |

Relationship between the two inputs and the output of the OR, AND, NOR and NAND logic operations

Any circuit can be built using the fundamental NOR and NAND logic

Murali, Sinha, Ditto & Bulsara, Physical Review Letters (2009) 104101

<ロ> (四) (四) (三) (三) (三)

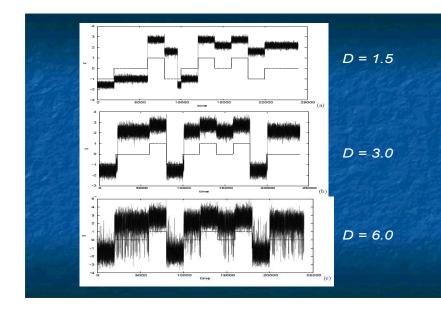

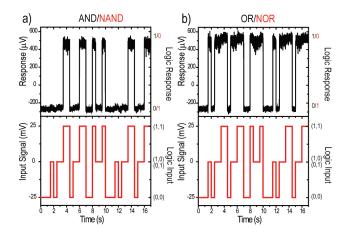

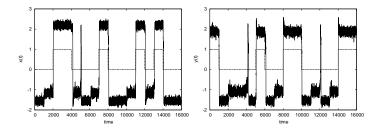

Input *I* is the sum of randomly switched square pulse trains

Different outputs obtained by driving the state of the system to one or the other well

For optimal noise intensity (center panel) a reliable NOR/OR gate is obtained

The crucial observation is that this logic output is obtained consistently and robustly only in an optimal window of noise

- For very small or very large noise the system does not yield any consistent logic output

- But in a reasonably wide band of moderate noise, the system produces the desired logical outputs consistently

- Verified in proof-of-principle circuit experiments

Effect of an additional constant bias C:

$$\frac{dx}{dt} = F(x) + I + C + D\eta(t)$$

Effect of bias : changes the symmetry of the potential wells

Acts as a "lever"

Varying bias C allows us to morph between NOR/OR and NAND/AND logic functions

2

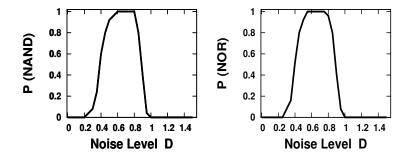

Quantify the consistency (or reliability) of obtaining a given logic output:

Calculate the probability of obtaining the desired logic output for different input sets

This probability, P(logic), is the ratio of the number of correct logic outputs to the total number of runs

Each run samples over the four possible inputs (0,0), (0,1), (1,0), (1,1), in different permutations

When P(logic) is close to 1 the logic operation is obtained very reliably

▲圖▶ ★ 国▶ ★ 国▶

Evident that the fundamental logic operation NAND and NOR is realized consistently in an optimal band of moderate noise

- Remarkable thing here then is that these stable consistent logic outputs are only realized in the presence of noise

- More specifically, in relatively wide windows of moderate noise, the system yields logic operations with near certain probability i.e., P(logic) ~ 1

- Occurrence of a flat maximum :

Logic Response is almost 100% accurate in a wide window of the noise

It is clear that, somewhat counterintuitively, noise plays a constructive role in obtaining a large, robust, asymmetric response to input signals

i.e. different (and distinct) levels of input pulses yield a 0/1 output, determined by the system being in either one of the two widely separated wells

This kind of response is necessary for logic operations, as it allows one to consistently map different distinct inputs to a binary output

Such mappings can be obtained, in principle, for any multiple-input logic operation by an appropriate choice of parameters

Probability of obtaining the NAND and NOR logic operations as functions of the noise intensity D (x-axis) and asymmetrizing dc input C (y-axis)

Murali, Sinha, Ditto & Bulsara, Physical Review Letters (2009) 104101

So one can morph between logic responses by simply adjusting the bias in a suitable window of noise

This has been demonstrated, explicitly, in our electronic analog realization

# Demonstrate the generality of the idea over a wide range of systems

< ≣ >

æ

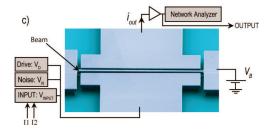

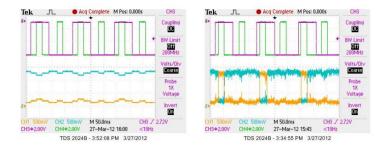

## Realization of reliable and flexible logic gates using CMOS based nonlinear circuits

CMOS-transistors produce a cubic-like nonlinearity:

Circuit is simple, robust, and capable of operating in very high frequency regimes

Further, its ease of implementation with integrated circuits and nanoelectronic devices should prove very useful in the context of reliable logic gate implementation in the presence of circuit noise

with K. Murali, I.R. Mohamed, W.L. Ditto & A.R. Bulsara, Applied Physics Letters (2009)

Showed how this system directly implements a Memory Device: Set-Reset latch

Vivek Kohar and Sudeshna Sinha, Physics Letters A (2012)

Triple wells: manipulating the potential wells to obtain different logic gates, including XOR

R. Storni, H. Ando, K. Aihara, K. Murali and Sudeshna Sinha, Physics Letters A (2012)

-∢ ≣ ▶

æ

Nano Mechanical Oscillators operating in the nonlinear regime where two different vibrational states co-exist

#### A Noise-Assisted Reprogrammable Nanomechanical Logic Gate

Fabricated from single-crystal silicon using e-beam lithography and surface nanomachining

Size: 20  $\mu m$  long, 300 nanometers wide, 500 nanometer thick Power consumption estimate:  $\sim$  0.2 nano Watts

Guerra, Bulsara, Ditto, Sinha, Murali and Mohanty

Nano Letters (2010)

・ロト ・四ト ・ヨト ・ヨト

æ

Guerra, Bulsara, Ditto, Sinha, Murali, Mohanty, Nano Letters (2010) US Patent, 2013

< ∃ >

æ

Noise-induced Chemical Logic Gates

Consider a chemical reaction system asymmetrically perturbed by means of a very small bias in the racemization equilibrium between two enantiomers

with Buhse, Cruz & Parmananda Europhysics Letters (2009) In such systems, small additive noise amplifies the symmetry-breaking, and yields biased product distributions

- Our central idea here is to interpret this noise-induced product selection in this chemical system, as a logical operation

- That is, the correspondence between enantioselection, interpreted as an output, and noise intensity, interpreted as input, mimics the input-output relations of all fundamental logic gates

So different product selections have a one-to-one robust correspondence to the different logic outputs

Enhanced Symmetry-breaking : yielding logic output 1

No symmetry-breaking : corresponding to logic output 0

Logic Response Control:

Type of logic behaviour obtained, namely AND, OR, NOR, NAND, XOR, XNOR, can be controlled by additive noise level

So varying noise allows varying product distributions, and consequently different logic responses

Correspondence between the noise levels and the enantiomeric products, exactly mirrors the input-output relations of different fundamental logic gates

### Logical Stochastic Resonance in a Bistable Optical System

with Kamal P. Singh (Physical Review E, 2010)

d⊒ ▶ < ≣

< ≣ ▶

æ

Output : Instensity detected via a polarizer

Showed that the polarization dynamics of the bistable optical system mirrors a logic operation

As one increases the noise, the probability of the output reflecting the desired logic operation increases to nearly unity and then decreases

### Both multiplicative noise and additive noise were considered

Source of the multiplicative noise is electrical and due to feedback, while the source of the additive noise is magnetic

Highlighted the possibility of processing two complementary logic gates in parallel by exploiting two coupled orthogonal polarizations which can be detected simultaneously

Synthetic Gene Networks as flexible parallel Logic Gates

Robust logic outputs from a noisy biological system

with H. Ando, R. Storni and Kazu Aihara

Europhysics Letters (2011)

Chemical reactions describing this network, is given by suitable rescaling as:

$$\dot{x} = \frac{m(1+x^2+\alpha\sigma_1x^4)}{1+x^2+\sigma_1x^4+\sigma_1\sigma_2x^6} - \gamma x = F(x)$$

where x is the concentration of the repressor

Such equations often arise in modelling genetic circuits

In its functional form, the right hand side represents production of repressor due to transcription

Even polynomials in x arise due to dimerization and subsequent binding to the promoter region

For the operator region of  $\lambda$  phage,  $\sigma_1\sim$  2,  $\sigma_2\sim$  0.08 and  $\alpha\sim 11$

The integer m represents the number of plasmids per cell

It is possible to design a plasmid with a given copy number

The parameter  $\gamma$  is directly proportional to the protein degradation rate, and in the construction of artificial networks can be considered a tunable parameter

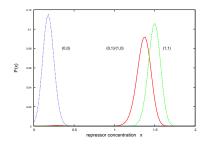

Nonlinearity leads to a double well potential, and different  $\gamma$  introduces varying degrees of asymmetry in the potential

- Yields robust logic output in optimal window of noise

- $\blacktriangleright$  Can switch logic function by changing  $\gamma$

Two coupled genetic networks

Toggle switch : composed of two repressors and and two constructive promoters

Each promoter is inhibited by the repressor that is transcribed by the opposing promoter

$$\dot{u} = \frac{\alpha_1}{1 + v^{n_1}} - d_1 u + g_1$$

$$\dot{v} = \frac{\alpha_2}{1 + u^{n_2}} - d_2 v + g_2$$

Dashed line shows the desired logic response (OR for the left panel and AND for the right panel)

Evidently, the left panel shows consistent  $\mathsf{OR}/\mathsf{NOR}$  and the right panel consistent  $\mathsf{AND}/\mathsf{NAND}$

Two gate operations can be achieved simultaneously

Ando, Sinha, Storni & Aihara, Europhysics Letters, 2011

#### Generalized Parallel Logic:

For example, consider the following 2-D system with independent sets of inputs  $I = I_1 + I_2$  and  $I' = I'_1 + I'_2$ :

$$\dot{x} = f(x) - y + h_1(I, I') + D\eta_1(t),$$

(1)

$$\dot{y} = x - g(y) + h_2(I, I') + D\eta_2(t),$$

(2)

where f, g are cubic functions:  $f(x) = a_1x^3 + b_1x^2 + c_1x + d_1$ ,  $g(y) = a_2y^3 + b_2y^2 + c_2y + d_2$

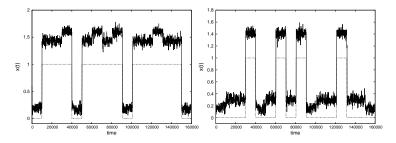

# Time series of x(t) (left) and y(t) (right)

AND for the left panel and XOR for the right panel

AND and XOR yield the ubiquitous Bit-by-Bit Addition

Indicates the parallel processing potential

- Synthetic gene network can function, in an optimal window of noise, as a robust logic gate

- Higher dimensional system for parallel processing logic functions

- Indicates that more complex systems may have inherently greater computational capability arising from greater parallel processing capacity

One can also analyse the probability P(x) of obtaining the system in state x by solving for the steady state distribution arising from the relevant Fokker Planck equation, namely  $P(x) = A \exp(-2\phi(x)/D)$  where A is a normalization constant, D

is noise intensity and  $-\partial \phi(x)/\partial x = F(x)$

This analysis yields results completely consistent with the observations

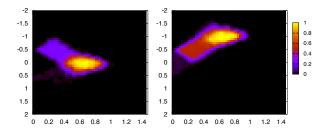

P(x) vs x, for different input sets, reflecting a clean OR/NOR logic association

# Electronic Analog of Synthetic Genetic Networks

Good agreement between circuit measurements and prediction

with Ed Hellen, S.K. Dana & J. Kurths

<ロト <回ト < 三ト

- ∢ ≣ ▶

Sudeshna Sinha Noisy Logic

◆□ → ◆□ → ◆三 → ◆三 → ● ● ● ● ●

Examples of work coming in from other groups following this concept:

Compact three-terminal Resonant Tunneling Diode

Worschech et al, Applied Physics Lettes, 2010

Vertical cavity surface emitting lasers (VCSEL)

Zamora-Munt and Masoller, Optics Express, 2010

## Thin Films

Kanki et al, Applied Physics Letters, 2010

-<- ⊒ →

2

Demonstrated the possibility of obtaining phenomena analogous to Logical Stochastic Resonance under rapidly varying regular forcing, such as sinusoidal driving or rectangular pulse trains

Driving frequency plays the role of strength of noise

Optimal performance : in a window of forcing frequency

Corroborated by circuit experiments

with Gupta, Sohane, Kohar & Murali Physical Review E (Rapid Communication), November 2011

## Bottomline ... and Outreach ...

Exploit the effect of noise on nonlinear systems in order to extract different desired responses

Interplay of noise and nonlinearity can enhance "logical" responses

- < ∃ →

æ

### Noise Assisted Computation:

- Shown how the interplay between a noise-floor and nonlinearity can be exploited for the design of key logic-gate structures

- Specifically we have shown the direct and flexible implementation of the fundamental logic gates, NOR and NAND, in an optimal band of noise, from which any universal computing device can be constructed

- Switching of logic functions by using the nonlinearity as a logic response controller

#### Murali & SS

Exploiting the effect of noise on nonlinear systems to obtain reconfigurable logic gates *Nonlinear Dynamics*, Ed. M. Daniel and S. Rajasekar (Narosa, 2009)

Murali, SS, Ditto & Bulsara Reliable Logic Circuit Elements that Exploit Nonlinearity in the Presence of a Noise-Floor Physical Review Letters (2009) 104101

Featured in Physical Review Focus

- SS, Cruz, Buhse & Parmananda Exploiting the effect of noise on a chemical system to obtain logic gates Europhysics Letters (2009) 60003

- Murali, Mohamed, SS, Ditto & Bulsara Realization of reliable and flexible logic gates using noisy nonlinear circuits Applied Physics Letters (2009) 194102

- Guerra, Bulsara, Ditto, SS, Murali & Mohanty A Noise-Assisted Reprogrammable Nanomechanical Logic Gate Nano Letters (2010) 1168

- Ando, SS, Storni & Aihara, Synthetic Gene Networks as flexible parallel Logic Gates Europhysics Letters, 2011

Phys. Rev. Lett. 102, 104101

(issue of 13 March 2009) Reliable Logic Circuit Elements That Exploit Nonlinearity the Presence of a Noise Floor k. Murali, Sudeshna Sinha, William L. Ditto, and Adi R. Bulsara

**Noisy Logic**

<sub>in</sub>5 March 2009

#### New circuits feed on noise

Digital circuits turn buzzing environments into an advantage

・ロト ・回ト ・ヨト ・ヨトー

3

By <u>Solmaz Barazesh</u> Web Edition: 2:58 pm March 12, 2009